# High Voltage High Current LED Driver Controller for Buck, Boost or Buck-Boost Topology

## **General Description**

The RT8475 is a current mode PWM controller designed to drive an external MOSFET for high current LED applications. With a current sense amplifier threshold of 190mV, the LED current is programmable with one external current sense resistor. With the maximum operating input voltage of 36V and output voltage up to 90V, the RT8475 is ideal for buck, boost or buck-boost operation.

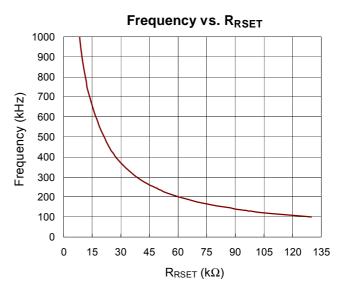

With the switching frequency programmable over 100kHz to 1MHz, the external inductor and capacitors can be small while maintaining high efficiency.

Dimming can be done by either analog or digital. The builtin clamping comparator and filter allow easy low noise analog dimming conversion from digital signal with only one external capacitor.

The RT8475 is available in SOP-14 and WQFN-16L 3x3 packages.

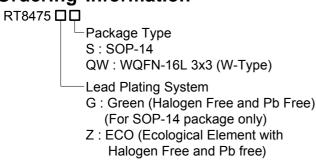

## **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- High Voltage Capability: V<sub>IN</sub> Up to 36V, LED Sensing Threshold Common Mode Voltage Up to 90V

- Buck, Boost or Buck-Boost Operation

- Programmable Switching Frequency

- Easy Dimming Control: Analog or Digital Converting to Analog with One External Capacitor

- Programmable Soft-Start to Avoid Inrush Current

- Programmable Over Voltage Protection

- V<sub>IN</sub> Under Voltage Lockout and Thermal Shutdown

- RoHS Compliant and Halogen Free

## **Applications**

- General Industrial High Power LED Lighting

- · Desk Lights and Room Lighting

- · Building and Street Lighting

- Industrial Display Backlight

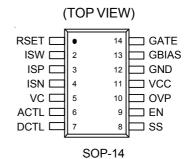

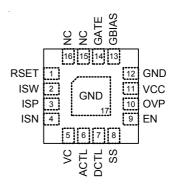

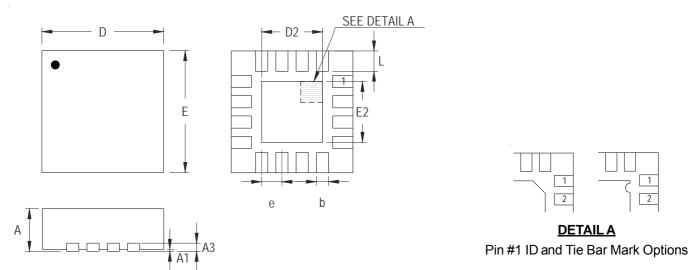

## **Pin Configurations**

WQFN-16L 3x3

Copyright ©2016 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Marking Information**

RT8475GS

RT8475 GSYMDNN RT8475GS: Product Number

YMDNN: Date Code

5A YM DNN

5A: Product Code YMDNN: Date Code

RT8475ZS

RT8475 ZSYMDNN RT8475ZS: Product Number

YMDNN: Date Code

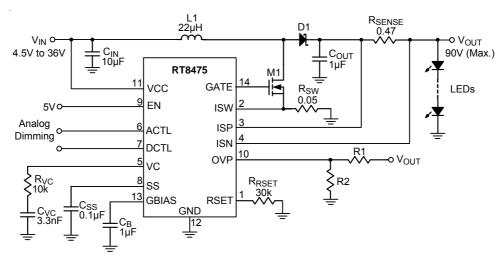

# **Typical Application Circuit**

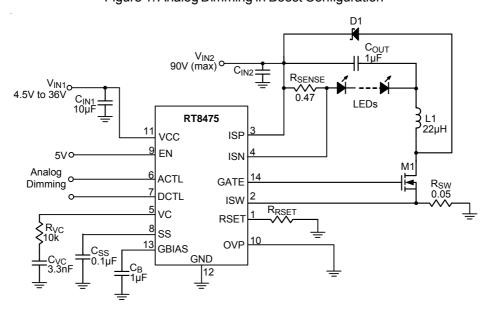

Figure 1. Analog Dimming in Boost Configuration

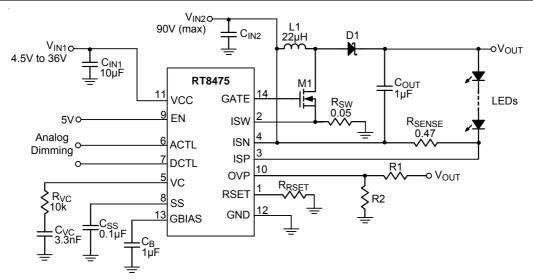

Figure 2. Analog Dimming in Buck Configuration

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Figure 3. Analog Dimming in Buck-Boost Configuration

# **Functional Pin Description**

| Pin No. |                         | Din Nama | Din Franction                                                                                                                                                         |  |  |

|---------|-------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SOP-14  | WQFN-16L 3x3            | Pin Name | Pin Function                                                                                                                                                          |  |  |

| 1       | 1                       | RSET     | Switch Frequency Set Pin. Connect a resistor from RSET to GND.<br>$R_{RSET}$ = 30k $\Omega$ will set $f_{SW}$ = 350kHz.                                               |  |  |

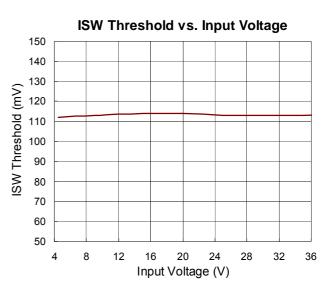

| 2       | 2                       | ISW      | External MOSFET Switch Current Sense. Connect the current sense resistor between external N-MOSFET switch and the ground.                                             |  |  |

| 3       | 3                       | ISP      | LED Current Sense Amplifier Positive Input with Common Mode Up to 90V.                                                                                                |  |  |

| 4       | 4                       | ISN      | LED Current Sense Amplifier Negative Input. Voltage threshold between ISP and ISN is 190mV with common mode voltage up to 90V.                                        |  |  |

| 5       | 5                       | VC       | PWM Control Loop Compensation.                                                                                                                                        |  |  |

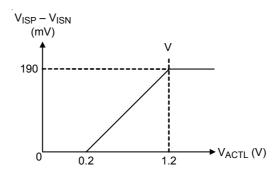

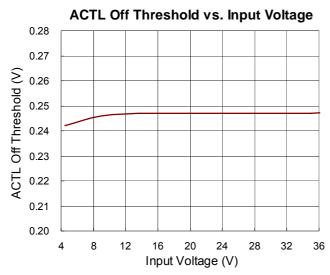

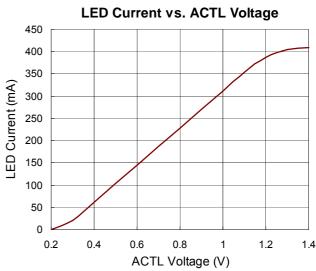

| 6       | 6                       | ACTL     | Analog Dimming Control. The effective programming voltage range of the pin is between 0.2V and 1.2V.                                                                  |  |  |

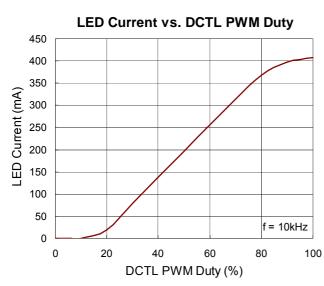

| 7       | 7                       | DCTL     | By adding a $0.47\mu F$ filtering capacitor on ACTL pin, the PWM dimming signal on DCTL pin can be averaged and converted into analog dimming signal on the ACTL pin. |  |  |

| 8       | 8                       | SS       | Soft-Start. A capacitor of at least 10nF is required for proper soft-start.                                                                                           |  |  |

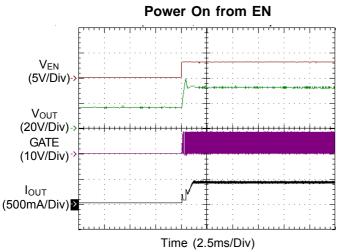

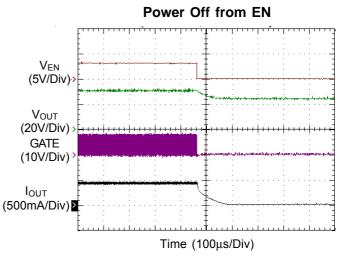

| 9       | 9                       | EN       | Chip Enable (Active High). When this pin voltage is low, the chip is in shutdown mode.                                                                                |  |  |

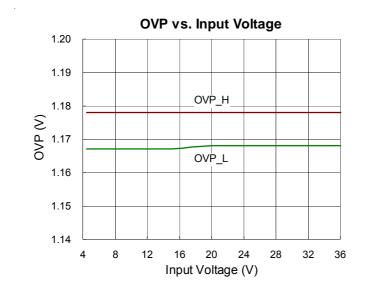

| 10      | 10                      | OVP      | Over Voltage Protection. The PWM converter turns off when the voltage of the pin goes to higher than 1.18V.                                                           |  |  |

| 11      | 11                      | VCC      | Power Supply Pin of the Chip. For good bypass, a low ESR capacitor is required.                                                                                       |  |  |

| 12      | 12,<br>17 (Exposed Pad) | GND      | Ground. The Exposed Pad must be Soldered to a Large PCB and Connected to GND for Maximum Power Dissipation.                                                           |  |  |

| 13      | 13                      | GBIAS    | Internal Gate Driver Bias. A good bypass capacitor is required.                                                                                                       |  |  |

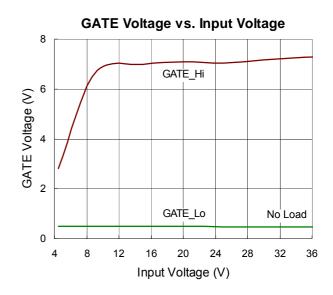

| 14      | 14                      | GATE     | External MOSFET Switch Gate Driver Output.                                                                                                                            |  |  |

|         | 15, 16                  | NC       | No Internal Connection.                                                                                                                                               |  |  |

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Function Block Diagram**

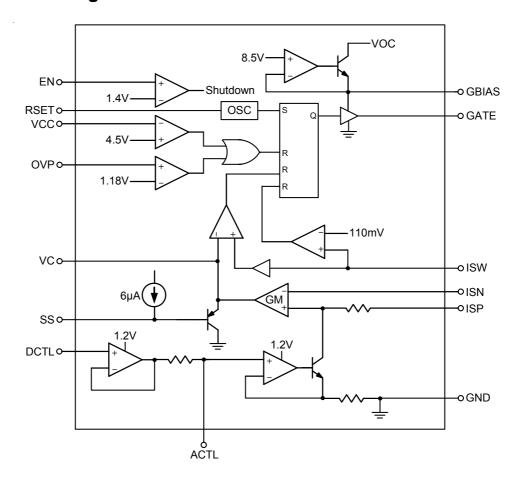

Figure 4

## Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VCC                                                   | –0.3 to 38V    |

|-----------------------------------------------------------------------------|----------------|

| • GBIAS, GATE                                                               | –0.3 to 10V    |

| • ISW                                                                       | –0.3 to 1V     |

| • ISP, ISN                                                                  | –0.3 to 100V   |

| • DCTL, ACTL, OVP (Note 2)                                                  | –0.3 to 8V     |

| • EN                                                                        | –0.3 to 20V    |

| • SS, RSET, VC                                                              | –0.3 to 5V     |

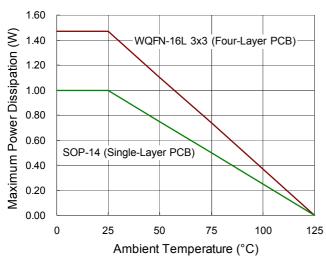

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| SOP-14                                                                      | 1.0W           |

| WQFN-16L 3x3                                                                | 1.471W         |

| Package Thermal Resistance (Note 3)                                         |                |

| SOP-14, θ <sub>JA</sub>                                                     | 100°C/W        |

| WQFN-16L 3x3, $\theta_{JA}$                                                 | 68°C/W         |

| WQFN-16L 3x3, $\theta_{JC}$                                                 | 7.5°C/W        |

| Junction Temperature                                                        | 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| Storage Temperature Range                                                   | –65°C to 150°C |

| ESD Susceptibility (Note 4)                                                 |                |

| HBM (Human Body Model)                                                      | 2kV            |

| MM (Machine Model)                                                          | 200V           |

|                                                                             |                |

# **Recommended Operating Conditions** (Note 5)

• Supply Input Voltage Range, VCC------ 4.5V to 36V

• Junction Temperature Range ----- --- -40°C to 125°C

## **Electrical Characteristics**

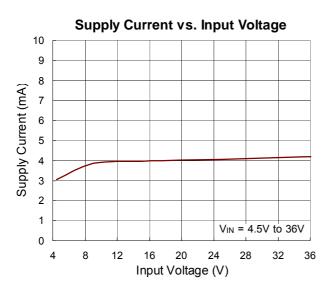

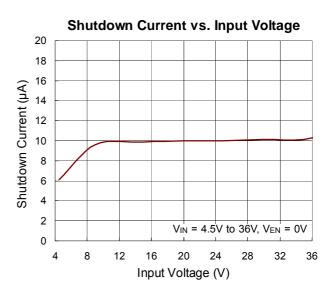

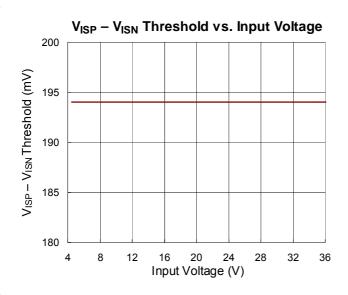

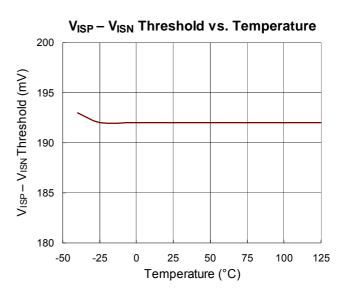

( $V_{CC}$  = 24V, No Load on any Output,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                                              |            | Symbol           | Test Conditions                                                           | Min | Тур | Max | Unit |  |

|--------------------------------------------------------|------------|------------------|---------------------------------------------------------------------------|-----|-----|-----|------|--|

| Overall                                                |            |                  |                                                                           |     |     |     |      |  |

| Supply Current                                         |            | lvcc             | V <sub>VC</sub> ≤ 0.4V (Switching off)                                    |     | 6   | 7.2 | mA   |  |

| Shutdown Current                                       |            | Ishdn            | V <sub>EN</sub> ≤ 0.7V                                                    |     | 12  |     | μΑ   |  |

| EN Threshold<br>Voltage                                | Logic-High | VIH              |                                                                           | 2   |     |     | V    |  |

|                                                        | Logic-Low  | VIL              |                                                                           |     |     | 0.5 |      |  |

| EN Input Current                                       |            |                  | V <sub>EN</sub> ≤ 3V                                                      |     |     | 1.2 | μΑ   |  |

| Current Sense                                          | Amplifier  |                  |                                                                           |     |     |     |      |  |

| Input Threshold (V <sub>ISP</sub> – V <sub>ISN</sub> ) |            |                  | $V_{ACTL} \ge 1.25V$ ,<br>$12V \le common \ mode \le 90V$                 | 182 | 190 | 198 | - mV |  |

|                                                        |            |                  | $1.25V \ge V_{ACTL} \ge 1.2V$ , (Note 7)<br>$12V \le common mode \le 90V$ |     | 188 |     |      |  |

| ISP Input Current                                      |            | I <sub>ISP</sub> | $4.5V \le V_{ISP} \le 90V$                                                |     | 140 |     | μΑ   |  |

| ISN Input Current                                      |            | I <sub>ISN</sub> | $4.5V \le V_{ISN} \le 90V$                                                |     | 60  |     | μΑ   |  |

| VC Output Current                                      |            | Ivc              | $0.5V \le V_C \le 2.4V$                                                   |     | ±20 |     | μΑ   |  |

| VC Threshold for PWM Switch Off                        |            |                  |                                                                           |     | 0.7 |     | V    |  |

Copyright ©2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                             | Symbol              | Test Conditions               | Min | Тур  | Max | Unit |

|---------------------------------------|---------------------|-------------------------------|-----|------|-----|------|

| LED Dimming                           |                     |                               |     |      |     |      |

| Analog Dimming ACTL Pin               | IACTL               | V <sub>ACTL</sub> = 1.2V      |     | 1    |     | μА   |

| Input Current                         |                     | V <sub>ACTL</sub> = 0.2V      |     | 10   |     |      |

| LED Current On Threshold at ACTL      | VACTL_On            |                               |     | 1.3  |     | ٧    |

| LED Current Off Threshold at ACTL     | VACTL_Off           |                               |     | 0.2  |     | ٧    |

| DCTL Input Current                    | IDCTL               | $0.3V \leq V_{DCTL} \leq 5V$  |     |      | 0.5 | μΑ   |

| DCTL Threshold Voltage                | V <sub>DCTL</sub> H | (Note 6)                      | 2   |      | -   | V    |

| DOTE Threshold voltage                | V <sub>DCTL_L</sub> | (Note 6)                      |     |      | 0.3 | V    |

| PWM Control                           |                     |                               |     |      |     |      |

| Switching Frequency                   | fsw                 | $R_{RSET} = 30k\Omega$        | 280 | 350  | 420 | kHz  |

| Minimum Off-Time                      |                     | $R_{RSET} = 30k\Omega$        |     | 250  |     | ns   |

| Switch Gate Driver                    |                     |                               |     |      |     |      |

| GBIAS Voltage                         | V <sub>GBIAS</sub>  | I <sub>GBIAS</sub> = 20mA     | 7.8 | 8.5  | 9.2 | V    |

| CATE Voltage Lligh                    | VGATE_H             | I <sub>GATE</sub> = -50mA     | 6   | 7.2  | 7.8 | V    |

| GATE Voltage High                     |                     | I <sub>GATE</sub> = -100μA    | 7.5 | 7.8  | 7.9 |      |

| CATE Voltage Law                      | V <sub>GATE_L</sub> | I <sub>GATE</sub> = 50mA      |     | 0.5  | 1   | V    |

| GATE Voltage Low                      |                     | I <sub>GATE</sub> = 100μA     |     | 0.1  | 0.9 |      |

| GATE Drive Rise and Fall Time         |                     | 1nF Load at GATE              |     | 20   | 100 | ns   |

| PWM Switch Current Limit<br>Threshold | Isw_LIM             |                               | 80  | 110  | 145 | mV   |

| OVP and Soft-Start                    |                     |                               |     |      |     |      |

| OVP Threshold                         | V <sub>OVP_th</sub> |                               |     | 1.18 |     | V    |

| OVP Input Current                     | IOVP                | $0.7V \leq V_{OVP} \leq 1.5V$ |     |      | 0.1 | μΑ   |

| Soft-Start Pin Current                | Iss                 | $V_{SS} \le 2V$               |     | 6    |     | μΑ   |

| Thermal Shutdown Protection           | T <sub>SD</sub>     |                               |     | 145  |     | °C   |

| Thermal Shutdown Hysteresis           | $\DeltaT_{SD}$      |                               |     | 10   |     | C    |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.** If connected with a  $20k\Omega$  serial resistor, ACTL and DCTL can go up to 36V.

- Note 3. For WQFN-16L 3x3,  $\theta_{JA}$  is measured in natural convection at  $T_A$  = 25°C on a high-effective thermal conductivity test board of JEDEC 51-7 thermal measurement standard. The measurement case position of  $\theta_{JC}$  is on the exposed pad of the package. For SOP-14,  $\theta_{JA}$  is measured in natural convection at  $T_A$  = 25°C on a low-effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. Devices are ESD sensitive. Handling precaution is recommended.

- Note 5. The device is not guaranteed to function outside its operating conditions.

- Note 6. Guaranteed by design, not subjected to production test.

- Note 7. The ACTL dimming curve is saturating when  $V_{ACTL} \ge 1.2V$ . Please refer to typical operation characteristics curve of  $I_{LED}$  vs.  $V_{ACTL}$ . This item is not subjected to production test.

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

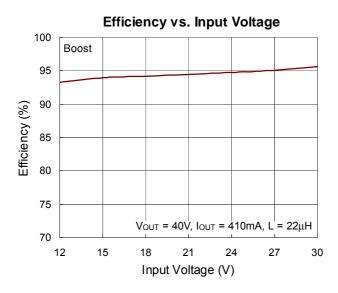

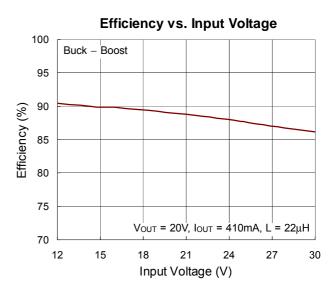

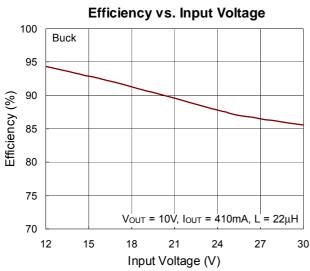

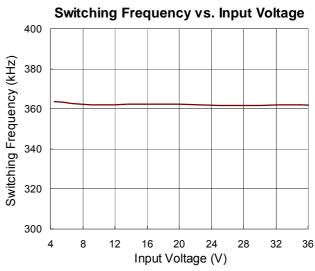

# **Typical Operating Characteristics**

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Applications Information**

The RT8475 is a current mode PWM controller designed to drive an external MOSFET for high current LED applications. The LED current can be programmed by an external resistor. The input voltage range of the RT8475 can be up to 36V and the output voltage can be up to 90V. The RT8475 provides analog and PWM dimming to achieve LED current control.

#### **GBIAS** Regulator and Bypass Capacitor

The GBIAS pin requires a capacitor for stable operation and to store the charge for the large GATE switching currents. Choose a 25V rated low ESR, X7R or X5R ceramic capacitor for best performance. The value of a  $1\mu$ F capacitor will be adequate for many applications.

Place the capacitor close to the IC to minimize the trace length to the GBIAS pin and also to the IC ground. An internal current limit on the GBIAS output protects the RT8475 from excessive on-chip power dissipation.

The GBIAS pin has its own under-voltage disable (UVLO) set to 4.3V(typical) to protect the external FETs from excessive power dissipation caused by not being fully enhanced. If the input voltage, VIN, will not exceed 8V, then the GBIAS pin should be connected to the input supply. Be aware if GBIAS supply is used to drive extra circuits besides RT8475, typically the extra GBIAS load should be limited to less than 10mA.

#### **Loop Compensation**

The RT8475 uses an internal error amplifier whose compensation pin (VC) allowing the loop response optimized for specific application. The external inductor, output capacitor and the compensation resistor and capacitor determine the loop stability. The inductor and output capacitor are chosen based on performance, size and cost. The compensation resistor and capacitor at VC are selected to optimize control loop response and stability. For typical LED applications, a 3.3nF compensation capacitor at VC is adequate, and a series resistor should always be used to increase the slew rate on the VC pin to maintain tighter regulation of LED current during fast transients on the input supply to the converter an external resistor in series with a capacitor is connected

from the VC pin to GND to provide a pole and a zero for proper loop compensation. The typical compensation for the RT8475 is  $10k\Omega$  and 3.3nF.

#### Soft-Start

The soft-start of the RT8475 can be achieved by connecting a capacitor from SS pin to GND. The built-in soft-start circuit reduces the start-up current spike and output voltage overshoot. The soft-start time is determined by the external capacitor charged by an internal 6µA constant charging current. The SS pin directly limits the rate of voltage rise on the VC pin, which in turn limits the peak switch current.

The soft-start interval is set by the soft-start capacitor selection according to the equation:

$$t_{SS} = C_{SS} \times \frac{2.4V}{6\mu A}$$

A typical value for the soft-start capacitor is 0.1μF. The soft-start capacitor is discharged when EN/UVLO falls below its threshold, during an over temperature event or during an GBIAS under voltage event.

#### **LED Current Setting**

The LED current is programmed by placing an appropriate value current sense resistor between the ISP and ISN pins. Typically, sensing of the current should be done at the top of the LED string. The ACTL pin should be tied to a voltage higher than 1.2V to get the full-scale 190mV (typical) threshold across the sense resistor. The ACTL pin can also be used to dim the LED current to zero, although relative accuracy decreases with the decreasing voltage sense threshold. When the ACTL pin voltage is less than 1.2V, the LED current is:

$$I_{LED} = \frac{(V_{ACTL} - 0.2) \times 0.19}{R_{SENSE}}$$

Where,

R<sub>SENSE</sub> is the resistor between ISP and ISN.

When the voltage of ACTL is higher than 1.2V, the LED current is regulated to:

$$I_{LED(MAX)} = \frac{190mV}{R_{SENSE}}$$

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

The ACTL pin can also be used in conjunction with a thermistor to provide over temperature protection for the LED load, or with a voltage divider to  $V_{\text{IN}}$  to reduce output power and switching current when  $V_{\text{IN}}$  is low. The presence of a time varying differential voltage signal (ripple) across ISP and ISN at the switching frequency is expected.

The amplitude of this signal is increased by high LED load current, low switching frequency and/or a smaller value output filter capacitor. The compensation capacitor on the VC pin filters the signal so the average difference between ISP and ISN is regulated on the user-programmed value.

#### **Programmable Switching Frequency**

The RSET frequency adjust pin allows the user to program the switching frequency from 100kHz to 1MHz for optimized efficiency and performance or external component size. Higher frequency operation allows for smaller component size but increases switching losses and gate driving current, and may not allow sufficiently high or low duty cycle operation. Lower frequency operation gives better performance but with larger external component size. For an appropriate R<sub>RSET</sub> resistor value see Table 1 or Figure 5. An external resistor from the RSET pin to GND is required-do not leave this pin open.

Table 1. Switching Frequency vs. R<sub>REST</sub> Value (1% Resistor)

| f <sub>OSC</sub> (kHZ) | R <sub>RSET</sub> (kΩ) |

|------------------------|------------------------|

| 1000                   | 8.34                   |

| 800                    | 11.41                  |

| 600                    | 16.68                  |

| 500                    | 20.9                   |

| 300                    | 38.04                  |

| 200                    | 60.35                  |

| 100                    | 130                    |

Figure 5. Switching Frequency vs. R<sub>RSET</sub>

#### **Output Over Voltage Setting**

The RT8475 is equipped with Over Voltage Protection (OVP) function. When the voltage at OVP pin exceeds a threshold of approximately 1.18V, the power switch is turned off. The power switch can be turned on again once the voltage at OVP pin drops below 1.18V. For the Boost and Buck-Boost application, the output voltage could be clamped at a certain voltage level. The OVP voltage can be set by the following equation:

Vout, ovp =

$$1.18 \times \left(1 + \frac{R1}{R2}\right)$$

Where,

R1 and R2 are the voltage dividers from  $V_{\text{OUT}}$  to GND with the divider center node connected to OVP pin.

#### **Over Temperature Protection**

The RT8475 has Over Temperature Protection (OTP) function to prevent the excessive power dissipation from overheating. The OTP function will shut down switching operation when the die junction temperature exceeds 145°C. The chip will automatically start to switch again when the die junction temperature cools off.

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

#### **Inductor Selection**

The converter operates in discontinuous conduction mode when the inductance value is less than the value LBCM. With an inductance greater than LBCM, the converter operates in Continuous Conduction Mode (CCM). The inductance LBCM is determined by the following equations.

For Buck application:

$$L_{BCM} = \frac{V_{OUT}}{2 \times I_{OUT} \times f} \times \left(\frac{V_{IN} - V_{OUT}}{V_{IN}}\right)$$

For Boost application:

$$L_{BCM} = \frac{{V_{IN}}^2}{2 \times I_{OUT} \times f} \times \left( \frac{V_{OUT} - V_{IN}}{{V_{OUT}}^2} \right)$$

For Buck-Boost application:

$$L_{BCM} = \frac{{V_{IN}}^2}{2 \times I_{OUT} \times f} \times \frac{V_{OUT}}{\left(V_{IN} + V_{OUT}\right)^2}$$

where

$V_{OUT}$  = output voltage.

$V_{IN}$  = input voltage.

f = operating frequency.

$I_{OUT}$  = LED current.

Choose an inductance based on the operating frequency, input voltage and output voltage to provide a current mode ramp signal during the MOSFET on period for PWM control loop regulation. The inductance also determines the inductor ripple current. Operating the converter in CCM is recommended, which will have the smaller inductor ripple current and hence the less conduction losses from all converter components.

As a design example, to design the peak to peak inductor ripple to be  $\pm 30\%$  of the output current, the following equations can be used to estimate the size of the needed inductance:

For Buck application:

$$L = \frac{V_{OUT}}{2 \times 0.3 \times I_{OUT} \times f} \times \left(\frac{V_{IN} - V_{OUT}}{V_{IN}}\right)$$

For Boost application:

$$L = \frac{V_{IN}^{2}}{2 \times 0.3 \times I_{OUT} \times f} \times \left(\frac{V_{OUT} - V_{IN}}{V_{OUT}^{2}}\right)$$

For Buck-Boost application

$$L = \frac{V_{IN}^{2}}{2 \times 0.3 \times I_{OUT} \times f} \times \frac{V_{OUT}}{(V_{IN} + V_{OUT})^{2}}$$

The inductor must also be selected with a saturation current rating greater than the maximum inductor current during normal operation. The maximum inductor current can be calculated by the following equations.

For Buck application:

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT}}{2 \times L \times f} \times \left(\frac{V_{IN} - V_{OUT}}{V_{IN}}\right)$$

For Boost application:

$$I_{PEAK} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}} + \frac{V_{IN}}{2 \times L \times f} \times \left(\frac{V_{OUT} - V_{IN}}{V_{OUT}}\right)$$

For Buck-Boost application:

$$I_{PEAK} = \frac{\left(V_{IN} + V_{OUT}\right) \times I_{OUT}}{\eta \times V_{IN}} + \frac{V_{IN}}{2 \times L \times f} \times \left(\frac{V_{OUT}}{V_{IN} + V_{OUT}}\right)$$

$\eta$  is the efficiency of the power converter.

## **Power MOSFET Selection**

For applications operating at high input or output voltages, the power N-MOS FET switch is typically chosen for drain voltage VDS rating and low gate charge. Consideration of switch on-resistance, R<sub>DS(ON)</sub>, is usually secondary because switching losses dominate power loss. The GBIAS regulator on the RT8475 has a fixed current limit to protect the IC from excessive power dissipation at high VIN, so the N-MOSFET should be chosen so that the product of Qg at 5V and switching frequency does not exceed the GBIAS current limit.

#### **ISW Sense Resistor Selection**

The resistor,  $R_{SW}$ , between the Source of the external N-MOSFET and GND should be selected to provide adequate switch current to drive the application without exceeding the current limit threshold set by the ISW pin sense threshold of RT8475. The ISW sense resistor value can be calculated according to the formula below :

$$R_{SW} = \frac{\text{current limit threshold minimum value}}{I_{OCP}}$$

where  $I_{\text{OCP}}$  is about 1.33 to 1.5 times of inductor peak current  $I_{\text{PEAK}}$ .

The placement of  $R_{SW}$  should be close to the source of the N-MOSFET and the IC GND of the RT8475. The ISW pin input to RT8475 should be a Kelvin sense connection to the positive terminal of  $R_{SW}$ .

#### **Schottky Diode Selection**

The Schottky diode, with their low forward voltage drop and fast switching speed, is necessary for the RT8475 applications. In addition, power dissipation, reverse voltage rating and pulsating peak current are the important parameters for the Schottky diode selection. Choose a suitable Schottky diode whose reverse voltage rating is greater than maximum output voltage. The diode's average current rating must exceed the average output current. The diode conducts current only when the power switch is turned off (typically less than 50% duty cycle). If using the PWM feature for dimming, it is important to consider diode leakage, which increases with the temperature, from the output during the PWM low interval. Therefore, choose the Schottky diode with sufficiently low leakage current.

#### **Capacitor Selection**

The input capacitor reduces current spikes from the input supply and minimizes noise injection to the converter. For most of the RT8475 applications, a  $10\mu F$  ceramic capacitor is sufficient. A value higher or lower may be used depending on the noise level from the input supply and the input current to the converter.

In Boost application, the output capacitor is typically a ceramic capacitor and is selected based on the output voltage ripple requirements. The minimum value of the output capacitor  $C_{\text{OUT}}$  is approximately given by the following equation :

$$C_{OUT} = \frac{I_{OUT} \times V_{OUT}}{V_{IN} \times V_{RIPPLE} \times f_{SW}}$$

For LED applications, the equivalent resistance of the LED is typically low and the output filter capacitor should be sized to attenuate the current ripple. Use of X7R type ceramic capacitors is recommended. Lower operating frequencies will require proportionately higher capacitor values

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-16L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 68°C/W on a standard JEDEC 51-7 four-layer thermal test board. For SOP-14 package, the thermal resistance,  $\theta_{JA}$ , is 100°C/W on a standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (68°C/W) = 1.471W for WQFN-16L 3x3 package

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (100^{\circ}C/W) = 1.0W$  for SOP-14 package

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{\mathsf{J}(\mathsf{MAX})}$  and thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 6 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 6. Derating Curve of Maximum Power Dissipation

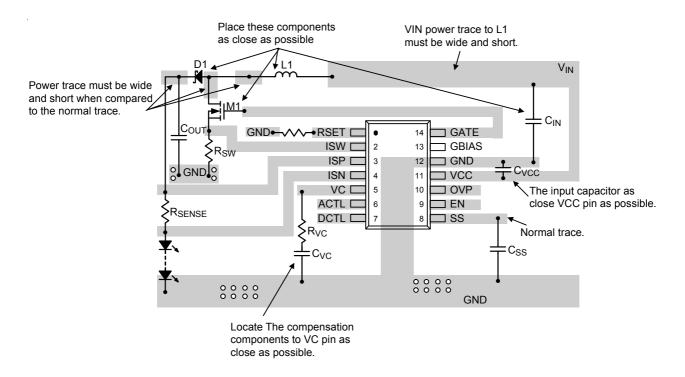

#### **Layout Consideration**

PCB layout is very important to design power switching converter circuits. The layout guidelines are suggested as follows:

- ► The power components L1, D1, C<sub>IN</sub>, M1 and C<sub>OUT</sub> must be placed as close to each other as possible to reduce the ac current loop area. The PCB trace between power components must be as short and wide as possible due to large current flow through these traces during operation.

- ▶ The input capacitor C<sub>VCC</sub> must be placed as close to VCC pin as possible.

- ▶ Place the compensation components to VC pin as close as possible to avoid noise pick up.

- Connect GND pin and Exposed Pad to a large ground plane for maximum power dissipation and noise reduction.

Figure 7. PCB Layout Guide

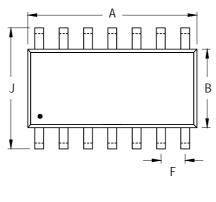

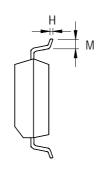

# **Outline Dimension**

| Compleal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|----------|--------------|---------------|----------------------|-------|--|

| Symbol   | Min          | Max           | Min                  | Max   |  |

| А        | 8.534        | 8.738         | 0.336                | 0.344 |  |

| В        | 3.810        | 3.988         | 0.150                | 0.157 |  |

| С        | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D        | 0.330        | 0.508         | 0.013                | 0.020 |  |

| F        | 1.194        | 1.346         | 0.047                | 0.053 |  |

| Н        | 0.178        | 0.254         | 0.007                | 0.010 |  |

| I        | 0.102        | 0.254         | 0.004                | 0.010 |  |

| J        | 5.791        | 6.198         | 0.228                | 0.244 |  |

| М        | 0.406        | 1.270         | 0.016                | 0.050 |  |

14-Lead SOP Plastic Package

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

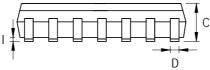

| Complete | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|----------|------------|----------------|----------------------|-------|--|

| Symbol   | Min        | Max            | Min                  | Max   |  |

| А        | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1       | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3       | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b        | 0.180      | 0.300          | 0.007                | 0.012 |  |

| D        | 2.950      | 3.050          | 0.116                | 0.120 |  |

| D2       | 1.300      | 1.750          | 0.051                | 0.069 |  |

| Е        | 2.950      | 3.050          | 0.116                | 0.120 |  |

| E2       | 1.300      | 1.750          | 0.051                | 0.069 |  |

| е        | 0.500      |                | 0.020                |       |  |

| L        | 0.350      | 0.450          | 0.014                | 0.018 |  |

W-Type 16L QFN 3x3 Package

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.